Page 86 - 2025年第56卷第6期

P. 86

式中 s和 s为计算单元边界两侧的波速并由下式计算:

- + n

{ s= min (u- gh ,u- c) (10)

槡

s

s

-

-

-

n

s= max (u+ gh ,u+ c)

槡

s

+

+

s

+

n

n

n

n

n

n

式中:u、u为计算单元 边 界 两 侧 的 法 向 速 度;u= (u + u)?2 + ( gh - gh );c= (u - u)?4 +

槡

槡

+

s

s

-

+

+

-

+

-

-

[26 - 27]

( gh + gh )?2。对于干单元的情况,波速可以用下式计算 :

槡

槡

-

+

n

{ s= u- gh -

槡

-

-

边界正向一侧为干单元: n

s= u+ 2 gh

+ + 槡 -

(11)

n

{ s= u- 2 gh +

槡

-

-

边界负向一侧为干单元: s= u+ gh +

n

槡

+

+

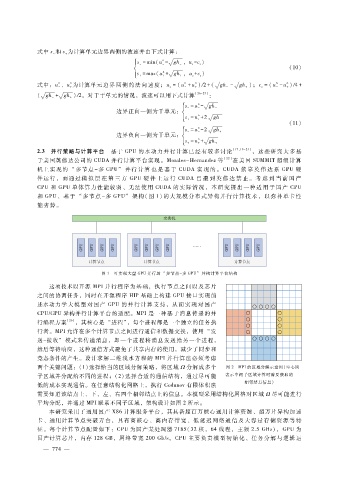

2.3 并行策略与计算平台 基于 GPU的水动力并行计算已经有较多讨论 [17,19 - 21] ,这些研究大多基

于美国英伟达公司的 CUDA并行计算平台实现。Morales - Hernandez等 [22] 在美国 SUMMIT超级计算

机上实现的 “多节点 - 多 GPU” 并行 计 算 也 是 基 于 CUDA实 现 的。 CUDA依 靠 英 伟 达 系 GPU硬

件运行,而通过 模 拟 层 在 第 三 方 GPU硬 件 上 运 行 CUDA已 遭 到 英 伟 达 禁 止。 考 虑 到 当 前 国 产

CPU和 GPU单体算力性能较弱、无法使用 CUDA的 实 际 情 况, 本 研 究 提 出 一 种 适 用 于 国 产 CPU

和 GPU、基于 “多节点 - 多 GPU” 架构(图 1)的大规模分布式异构并行计算技术,以弥补单卡性

能劣势。

图 1 可实现大量 GPU并行的 “多节点- 多 GPU” 异构计算平台结构

这项技术以开源 MPI并行程序为基础,执行节点之间以及芯片

之间的协调任务,同时在开源程序 HIP基础上构建 GPU接口实现前

述水动力学 大 模 型 对 国 产 GPU的 并 行 计 算 支 持,从 而 实 现 对 国 产

CPU?GPU异构并行计算平台的适配。MPI是一种基于消息传递的并

行编程方案 [26] ,其核心是 “进程”,每个进程都是一个独立的任务执

行者。MPI允许在多个计算节点之间进行通信和数据交换,使用 “发

送- 接收” 模式来传递消息,即一个进程将消息发送给另一个进程,

然后等待响应,这种通信方式避免了共享内存的使用,减少了同步和

竞态条件的产生。设计求解二维浅水方程的 MPI并行算法必须考虑

两个关键问题:(1)选择恰当的区域分解策略,将区域 Ω分解成多个 图 2 MPI的区域分解示意图(空心圆

子区域并分配给不同的进程;( 2)选择合适的通信结构,通过尽可能 表示中间子区域计算时需要获取的

相邻结点信息)

低的成本实现通信。在任意结构化网格上,执行 Godunov有限体积法

需要知道该结点上、下、左、右四个相邻结点上的信息。本模型采用结构化网格对区域 Ω尽可能进行

平均分配,并通过 MPI联系不同子区域,架构设计如图 2所示。

本研究采用了通用国产 X86计算服务平台,其具备超百万核心通用计算资源、超万片异构加速

卡、通用计算节点突破万 台,具有 高核心、高内存 带宽、低 延 迟 网 络 通 信 及 大 容 量 存 储 资 源 等 特

征。每个计算节点配置如下:CPU为国产某处理器 7185(32核,64线程,主频 2.5GHz),GPU为

国产计算芯片,内存 128GB,网络带宽 200Gb?s。CPU主要负责模 型 初 始化、任 务 分 解与逻辑运

4

— 7 7 —